邢臺YXC有源晶振電話

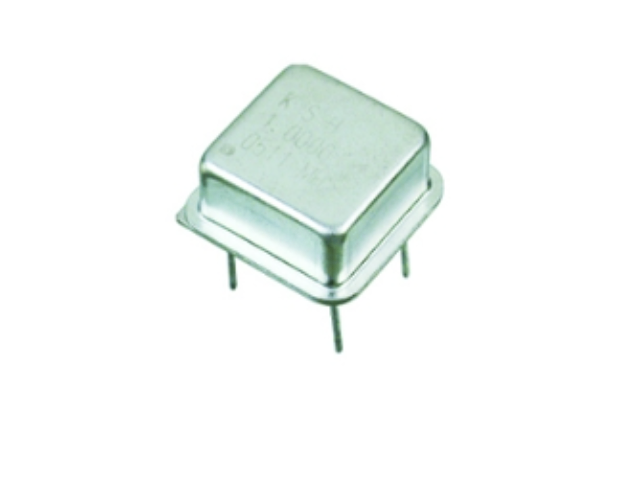

有源晶振能減少外部元件數量,源于其將時鐘信號生成、放大、穩壓等功能集成于單一封裝,直接替代傳統方案中需額外搭配的多類分立元件,從而大幅節省設備內部空間。傳統無源晶振只提供基礎諧振功能,需外部配套 4-6 個元件才能正常工作:包括反相放大器(如 CMOS 反相器芯片)實現信號振蕩、反饋電阻(Rf)與負載電容(Cl1/Cl2)校準振蕩頻率、LDO 穩壓器過濾供電噪聲、π 型濾波網絡(含電感、電容)抑制電源紋波。這些元件需在 PCB 上單獨布局,元件占用的 PCB 面積就達 8-15mm2(以 0402 封裝元件為例)。而有源晶振通過內置振蕩器、低噪聲晶體管放大電路、穩壓單元及濾波電容,只需 1 個封裝(常見尺寸如 3.2mm×2.5mm、2.0mm×1.6mm)即可實現同等功能,直接省去上述外部元件,單時鐘電路模塊的 PCB 空間占用可減少 60% 以上。有源晶振內置關鍵部件,無需用戶額外采購配套元件。邢臺YXC有源晶振電話

有源晶振的環境適應性調試已內置完成。面對溫度波動(如 - 40℃至 85℃工業場景),其溫補模塊(TCXO)或恒溫模塊(OCXO)已預設定補償曲線,用戶無需額外搭建溫度傳感器與補償電路,也無需在不同環境下測試頻率偏差并調整參數;標準化接口(如 LVDS、ECL)更省去接口適配調試,可直接對接 FPGA、MCU 等芯片。這種 “即插即用” 特性,將時鐘電路調試時間從傳統方案的 1-2 天縮短至幾分鐘,尤其降低非專業時鐘設計人員的技術門檻,同時避免因調試不當導致的系統時序故障。邢臺YXC有源晶振電話數據傳輸設備需精確時鐘,有源晶振可滿足其主要需求。

有源晶振能從電路設計全流程減少工程師的操作步驟,在于其集成化特性替代了傳統方案的多環節設計,直接壓縮開發周期,尤其適配消費電子、物聯網模塊等快迭代領域的需求。在原理圖設計階段,傳統無源晶振需工程師單獨設計振蕩電路(如 CMOS 反相器振蕩架構)、匹配負載電容(12pF-22pF)、反饋電阻(1MΩ-10MΩ),若驅動能力不足還需增加驅動芯片(如 74HC04),只時鐘部分就需繪制 10 余個元件的連接邏輯,步驟繁瑣且易因引腳錯連導致設計失效。而有源晶振內置振蕩、放大、穩壓功能,原理圖只需設計 2-3 個引腳(電源正、地、信號輸出)的簡單回路,繪制步驟減少 70% 以上,且無需擔心振蕩電路拓撲錯誤,降低設計返工率。

有源晶振的內置驅動設計還能保障信號完整性:其輸出端集成阻抗匹配電阻與信號整形電路,可減少信號傳輸中的反射與串擾,避免外部緩沖電路因阻抗不匹配導致的信號過沖、振鈴等問題。例如工業 PLC 需為 4 個 IO 控制模塊提供時鐘,有源晶振無需外接緩沖即可直接輸出穩定信號,省去緩沖芯片的 PCB 布局空間(約 3mm×2mm)與供電鏈路,同時避免外部緩沖引入的額外噪聲(相位噪聲可能增加 5-10dBc/Hz)。這種設計不僅簡化電路,更確保時鐘信號在多負載場景下的穩定性,適配消費電子、工業控制等多器件協同工作的需求。設計工業傳感器時,搭配有源晶振能提升信號穩定性。

在高精度場景中,時鐘信號的噪聲會直接影響系統性能,而有源晶振的低噪聲優勢能有效規避這一問題。從設計來看,有源晶振多采用低噪聲晶體管架構,如差分對管設計,可抑制共模噪聲干擾,同時通過負反饋電路控制信號放大過程,避免放大環節引入額外噪聲,其相位噪聲指標通常能達到 1kHz 偏移時低于 - 130dBc/Hz,遠優于無源晶振搭配外部電路的噪聲表現。對于 5G 通信基站這類高精度場景,信號解調對時鐘相位穩定性要求極高,若時鐘噪聲過大,會導致星座圖偏移,增加誤碼率。有源晶振內置的高精度晶體諧振器,能減少溫度、電壓波動引發的頻率漂移,配合電源濾波單元濾除供電鏈路的紋波噪聲,確保輸出時鐘信號的相位抖動控制在 1ps 以內,保障信號解調精度。有源晶振助力設備快速獲取時鐘信號,提升研發效率。邯鄲有源晶振現貨

有源晶振直接輸出時鐘信號,無需用戶進行額外信號處理。邢臺YXC有源晶振電話

有源晶振無需額外驅動部件即可工作,在于其內置振蕩器整合了 “信號生成 - 放大 - 穩定” 全流程功能,徹底替代傳統方案中需外接的驅動元件,從根源簡化電路設計。傳統無源晶振只包含石英晶體諧振單元,本身無法自主產生穩定時鐘信號,必須依賴外部驅動部件構建振蕩回路:需外接反相器芯片(如 74HCU04)提供振蕩所需的相位翻轉能力,搭配反饋電阻(1MΩ-10MΩ)維持振蕩幅度穩定,部分場景還需加功率放大管增強信號驅動能力 —— 這些驅動部件不僅占用 PCB 空間(約 5-8mm2),還需工程師反復調試元件參數(如反相器增益、電阻阻值),若參數不匹配易出現 “起振失敗” 或 “振蕩停擺”,尤其在低溫環境下,外部驅動元件性能下降可能導致時鐘中斷。邢臺YXC有源晶振電話

- 石家莊TXC有源晶振應用 2025-09-20

- 無錫揚興有源晶振廠家 2025-09-20

- 西安NDK有源晶振采購 2025-09-20

- 重慶YXC有源晶振代理商 2025-09-20

- 佛山YXC有源晶振多少錢 2025-09-20

- 肇慶NDK有源晶振價格 2025-09-20

- 邯鄲揚興有源晶振 2025-09-20

- 杭州揚興有源晶振廠家 2025-09-20

- 佛山有源晶振多少錢 2025-09-20

- 惠州KDS有源晶振 2025-09-20

- 嘉定區進口配電開關推薦廠家 2025-09-20

- 廣東光子面罩組裝 2025-09-20

- 石家莊矩形推拉自鎖連接器誠信合作 2025-09-20

- 江西無極變速金屬開關有哪些 2025-09-20

- 重慶雙端線束費用 2025-09-20

- 廣東常規PTC加熱片元件種類 2025-09-20

- 龍崗區OEM定制 2025-09-20

- 哪些是耐高溫膠帶哪家好 2025-09-20

- 甘肅電源系統防雷器廠家 2025-09-20

- 茂名三折屏LED顯示屏模組 2025-09-20