石家莊YXC有源晶振

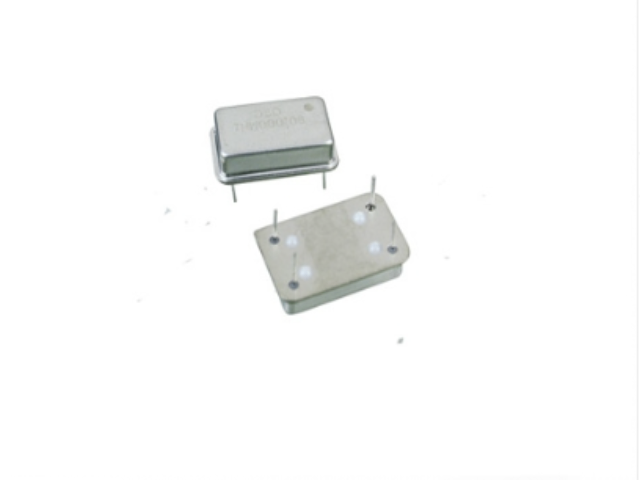

從電路構(gòu)成看,有源晶振集成低噪聲功率放大模塊與負(fù)載適配單元:放大模塊采用多級晶體管架構(gòu),可將晶體諧振產(chǎn)生的毫伏級微弱信號,線性放大至符合系統(tǒng)需求的標(biāo)準(zhǔn)幅度(如 3.3V CMOS 電平、5V TTL 電平),且放大過程中通過負(fù)反饋電路維持幅度穩(wěn)定,無需外部緩沖電路額外放大;負(fù)載適配單元則優(yōu)化了輸出阻抗(如匹配 50Ω/75Ω 傳輸阻抗),能直接驅(qū)動 3-5 個標(biāo)準(zhǔn) TTL 負(fù)載(或 2-3 個 LVDS 負(fù)載),即使同時為 MCU、射頻芯片、存儲模塊等多器件提供時鐘,也不會因負(fù)載增加導(dǎo)致信號幅度衰減或相位偏移 —— 而傳統(tǒng)無源晶振輸出信號驅(qū)動能力弱,若需驅(qū)動 2 個以上負(fù)載,必須外接緩沖芯片(如 74HC04),否則會出現(xiàn)信號失真。有源晶振無需緩沖電路,直接為設(shè)備提供合格時鐘信號。石家莊YXC有源晶振

有源晶振通過內(nèi)置設(shè)計完全替代上述調(diào)理功能:其一,內(nèi)置低噪聲放大電路,直接將晶體諧振的毫伏級信號放大至 1.8V-5V 標(biāo)準(zhǔn)電平(支持 CMOS/LVDS/TTL 多電平輸出),無需外接放大器與電平轉(zhuǎn)換芯片,適配不同芯片的電平需求;其二,集成 LDO 穩(wěn)壓單元與多級 RC 濾波網(wǎng)絡(luò),可將外部供電紋波(如 100mV)抑制至 1mV 以下,濾除 100MHz 以上高頻雜波,替代外部濾波與 EMI 抑制電路;其三,內(nèi)置阻抗匹配單元(可適配 50Ω/75Ω/100Ω 負(fù)載),無需外接匹配電阻,避免信號反射損耗。中山有源晶振批發(fā)有源晶振的便捷連接方式,降低用戶設(shè)備組裝難度。

有源晶振的環(huán)境適應(yīng)性調(diào)試已內(nèi)置完成。面對溫度波動(如 - 40℃至 85℃工業(yè)場景),其溫補模塊(TCXO)或恒溫模塊(OCXO)已預(yù)設(shè)定補償曲線,用戶無需額外搭建溫度傳感器與補償電路,也無需在不同環(huán)境下測試頻率偏差并調(diào)整參數(shù);標(biāo)準(zhǔn)化接口(如 LVDS、ECL)更省去接口適配調(diào)試,可直接對接 FPGA、MCU 等芯片。這種 “即插即用” 特性,將時鐘電路調(diào)試時間從傳統(tǒng)方案的 1-2 天縮短至幾分鐘,尤其降低非專業(yè)時鐘設(shè)計人員的技術(shù)門檻,同時避免因調(diào)試不當(dāng)導(dǎo)致的系統(tǒng)時序故障。

在信號放大與穩(wěn)幅環(huán)節(jié),內(nèi)置晶體管通過負(fù)反饋電路實現(xiàn)控制:晶體諧振器初始產(chǎn)生的振蕩信號幅度只為毫伏級,晶體管會對其進(jìn)行線性放大,同時反饋電路實時監(jiān)測輸出幅度,若幅度超出標(biāo)準(zhǔn)范圍(如 CMOS 電平的 3.3V±0.2V),則自動調(diào)整晶體管的放大倍數(shù),將幅度波動控制在 ±5% 以內(nèi),避免信號因幅度不穩(wěn)導(dǎo)致的時序誤判。此外,內(nèi)置晶體管還能保障振蕩的持續(xù)穩(wěn)定。傳統(tǒng)無源晶振依賴外部晶體管搭建振蕩電路,若外部元件參數(shù)漂移(如溫度導(dǎo)致的放大倍數(shù)下降),易出現(xiàn) “停振” 故障;而有源晶振的晶體管與振蕩電路集成于同一封裝,溫度、電壓變化時,晶體管的電學(xué)參數(shù)(如電流放大系數(shù) β)與振蕩電路的匹配度始終保持穩(wěn)定,可在 - 40℃~85℃寬溫范圍內(nèi)持續(xù)維持振蕩,確保輸出信號無中斷、無失真。這種穩(wěn)定性在工業(yè) PLC、5G 基站等關(guān)鍵設(shè)備中尤為重要,能直接避免因時鐘信號異常導(dǎo)致的系統(tǒng)停機或數(shù)據(jù)傳輸錯誤。連接有源晶振后,設(shè)備無需再配置復(fù)雜的信號調(diào)理電路。

低功耗設(shè)計適配物聯(lián)網(wǎng)設(shè)備長續(xù)航需求。如 32.768KHz 有源晶振待機電流可低至 1.4uA,通過定時優(yōu)化設(shè)備喚醒周期,減少無效能耗。同時,內(nèi)置穩(wěn)壓濾波模塊濾除供電噪聲,在工業(yè)電磁環(huán)境中仍保持信號純凈,無需額外電源調(diào)理部件,契合傳感器節(jié)點小型化設(shè)計需求。此外,有源晶振的標(biāo)準(zhǔn)化接口(如 CMOS 輸出)可直接對接 MCU 與通信模塊,省去信號轉(zhuǎn)換電路,其 ±10 - 30ppm 的批量一致性更降低了大規(guī)模部署的調(diào)試成本,為物聯(lián)網(wǎng)設(shè)備的可靠運行提供堅實時鐘保障。有源晶振簡化系統(tǒng)設(shè)計,幫助企業(yè)降低生產(chǎn)成本。邯鄲KDS有源晶振代理商

有源晶振的易用性與穩(wěn)定性,使其成為電子設(shè)備部件。石家莊YXC有源晶振

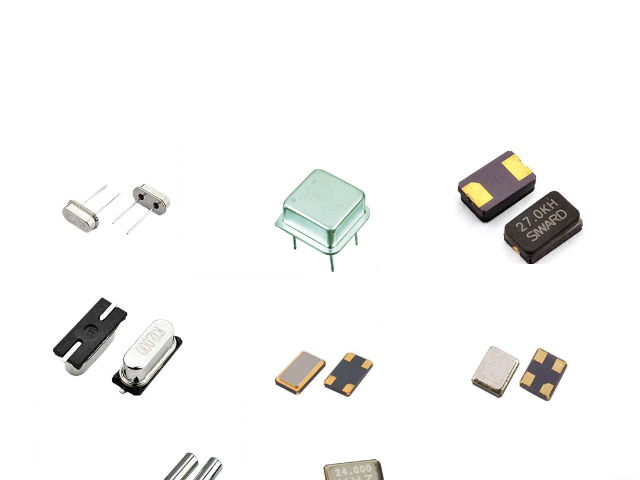

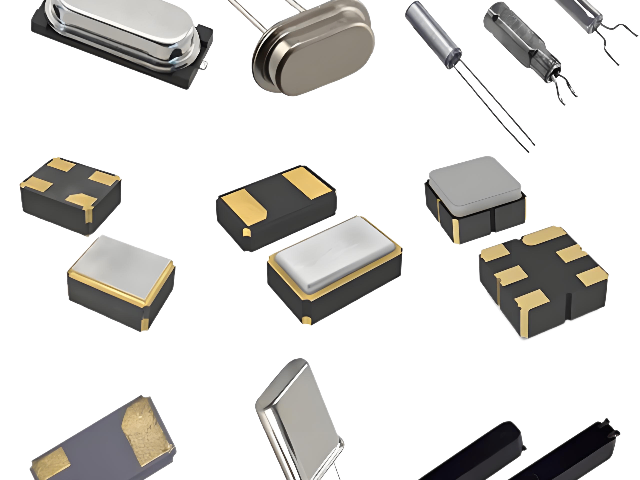

有源晶振無需額外驅(qū)動部件即可工作,在于其內(nèi)置振蕩器整合了 “信號生成 - 放大 - 穩(wěn)定” 全流程功能,徹底替代傳統(tǒng)方案中需外接的驅(qū)動元件,從根源簡化電路設(shè)計。傳統(tǒng)無源晶振只包含石英晶體諧振單元,本身無法自主產(chǎn)生穩(wěn)定時鐘信號,必須依賴外部驅(qū)動部件構(gòu)建振蕩回路:需外接反相器芯片(如 74HCU04)提供振蕩所需的相位翻轉(zhuǎn)能力,搭配反饋電阻(1MΩ-10MΩ)維持振蕩幅度穩(wěn)定,部分場景還需加功率放大管增強信號驅(qū)動能力 —— 這些驅(qū)動部件不僅占用 PCB 空間(約 5-8mm2),還需工程師反復(fù)調(diào)試元件參數(shù)(如反相器增益、電阻阻值),若參數(shù)不匹配易出現(xiàn) “起振失敗” 或 “振蕩停擺”,尤其在低溫環(huán)境下,外部驅(qū)動元件性能下降可能導(dǎo)致時鐘中斷。石家莊YXC有源晶振

- 石家莊TXC有源晶振應(yīng)用 2025-09-20

- 無錫揚興有源晶振廠家 2025-09-20

- 安徽揚興陶瓷晶振品牌 2025-09-20

- 秦皇島YXC有源晶振品牌 2025-09-20

- 西安NDK有源晶振采購 2025-09-20

- 重慶YXC有源晶振代理商 2025-09-20

- 佛山Y(jié)XC有源晶振多少錢 2025-09-20

- 蘭州KDS有源晶振批發(fā) 2025-09-20

- 肇慶NDK有源晶振價格 2025-09-20

- 邯鄲揚興有源晶振 2025-09-20

- 廣州低電容ESD二極管市場報價 2025-09-20

- INFIENON/英飛凌IRFP2907PBF代理商價格推薦 2025-09-20

- 杭州研祥一體機設(shè)計 2025-09-20

- 深圳多功能拖鏈廠家供應(yīng) 2025-09-20

- 220V時間繼電器廠家價格 2025-09-20

- 金華雙擺臂勻膠顯影機 2025-09-20

- 濟南工業(yè)級開發(fā)板 2025-09-20

- 閃光燈igbt 2025-09-20

- 工業(yè)交換機芯片通信芯片價格更新 2025-09-20

- 嘉定區(qū)進(jìn)口配電開關(guān)推薦廠家 2025-09-20