蘇州位算單元定制

位算單元與操作系統之間存在著密切的交互關系。操作系統作為管理計算機硬件和軟件資源的系統軟件,需要根據應用程序的需求,合理調度處理器的資源,其中就包括對位算單元的使用調度。當應用程序需要進行位運算操作時,會通過操作系統向處理器發出指令請求,操作系統會將該請求轉換為對應的機器指令,并分配處理器資源,讓位算單元執行相應的位運算。在多任務操作系統中,多個應用程序可能同時需要使用位算單元,操作系統需要采用合理的調度算法,如時間片輪轉調度、優先級調度等,協調不同任務對位算單元的使用,避免資源沖擊,確保每個任務都能得到及時的運算支持。此外,操作系統還會通過驅動程序與位算單元進行交互,對其進行初始化和配置,確保位算單元能夠正常工作,并向應用程序提供統一的接口,方便應用程序調用位算單元的功能。位算單元的動態功耗管理策略延長了設備續航時間。蘇州位算單元定制

位算單元的邏輯設計需要遵循嚴格的規范和標準。在位算單元的設計過程中,邏輯設計是關鍵環節,直接決定了位算單元的運算功能、速度和可靠性。設計人員需要根據處理器的整體需求,明確位算單元需要支持的位運算類型,如基本的與、或、非運算,以及移位、位計數、位反轉等復雜運算,并以此為基礎進行邏輯電路的設計。在設計過程中,需要遵循數字邏輯設計的規范,確保電路的邏輯正確性,同時考慮電路的延遲、功耗和面積等因素。例如,在設計加法器模塊時,需要在運算速度和電路復雜度之間進行平衡,選擇合適的加法器結構;在設計移位器時,需要確保移位操作的準確性和靈活性,支持不同位數的移位需求。此外,邏輯設計完成后,還需要通過仿真工具進行嚴格的驗證,確保位算單元在各種工況下都能正常工作,滿足設計指標。合肥Ubuntu位算單元批發位算單元如何實現AND/OR/XOR等基本邏輯運算?

位算單元的故障容錯技術是提高處理器可靠性的重要保障。在一些對可靠性要求極高的領域,如航空航天、醫療設備、工業控制等,即使位算單元出現輕微故障,也可能導致嚴重的后果,因此需要采用故障容錯技術,確保位算單元在出現故障時仍能正常工作或極小化故障影響。位算單元常用的故障容錯技術包括冗余設計、錯誤檢測與糾正(EDC/ECC)技術等。冗余設計是指在處理器中設置多個相同的位算單元,當主位算單元出現故障時,備用位算單元能夠立即接替工作,保證運算的連續性;錯誤檢測與糾正技術則是通過在數據中添加冗余校驗位,位算單元在運算過程中對數據進行校驗,檢測出數據傳輸或運算過程中出現的錯誤,并通過校驗位進行糾正。例如,在采用 ECC 內存的系統中,位算單元在處理內存中的數據時,能夠通過 ECC 校驗技術檢測并糾正單比特錯誤,避免錯誤數據影響運算結果。這些故障容錯技術的應用,大幅提高了位算單元的可靠性,滿足了高可靠性領域的應用需求。

位算單元與存儲器之間的協同工作對於計算機系統的性能至關重要。位算單元在進行運算時,需要從存儲器中讀取數據和指令,運算完成后,又需要將運算結果寫回存儲器。因此,位算單元與存儲器之間的數據傳輸速度和帶寬會直接影響位算單元的運算效率。如果數據傳輸速度過慢,位算單元可能會經常處于等待數據的狀態,無法充分發揮其運算能力,出現 “運算瓶頸”。為了解決這一問題,現代計算機系統通常會采用多級緩存架構,在處理器內部設置一級緩存、二級緩存甚至三級緩存,這些緩存的速度遠快于主存儲器,能夠將位算單元近期可能需要使用的數據和指令存儲在緩存中,減少位算單元對主存儲器的訪問次數,提高數據讀取速度。同時,通過優化存儲器的接口設計,提升數據傳輸帶寬,也能夠讓位算單元更快地獲取數據和存儲運算結果,實現位算單元與存儲器之間的高效協同,從而提升整個計算機系統的性能。AI加速器中位算單元如何優化神經網絡計算?

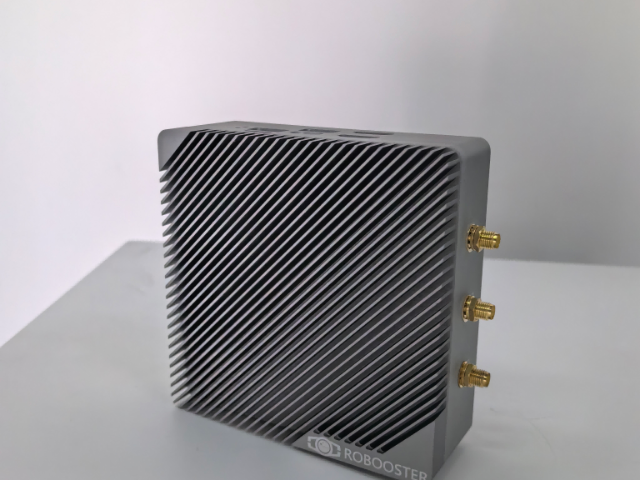

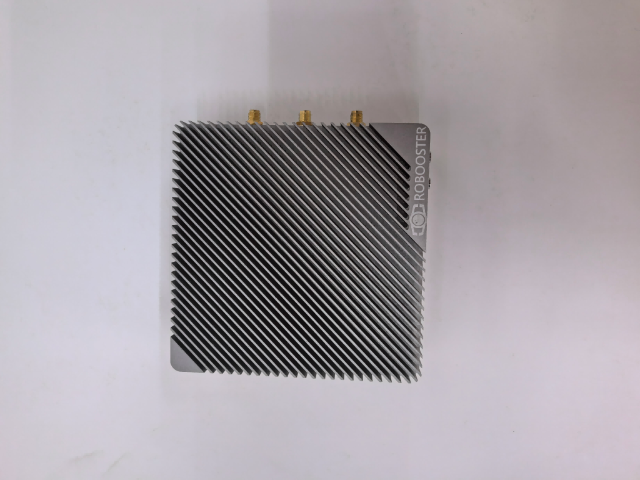

位算單元在教育領域也具有重要的教學價值。在計算機組成原理、數字邏輯電路等相關課程的教學中,位算單元是重要的教學案例和實踐對象。通過講解位算單元的工作原理、電路結構和運算過程,學生能夠更直觀地理解計算機如何處理二進制數據,以及硬件層面與軟件指令之間的關聯。例如,在數字邏輯電路實驗課中,學生可以通過搭建簡易的位算單元電路,親手操作與、或、非等邏輯門,觀察輸入不同二進制信號時的輸出結果,加深對邏輯運算的理解。此外,在計算機組成原理的課程設計中,學生還可以基于位算單元的原理,設計簡單的算術邏輯單元(ALU),將位運算與算術運算結合,進一步掌握計算機關鍵部件的設計思路。位算單元的教學不僅能夠幫助學生夯實專業基礎,還能培養學生的邏輯思維和實踐能力,為后續學習更復雜的計算機技術奠定基礎。位算單元集成了溫度傳感器,實現智能散熱控制。北京ROS位算單元方案

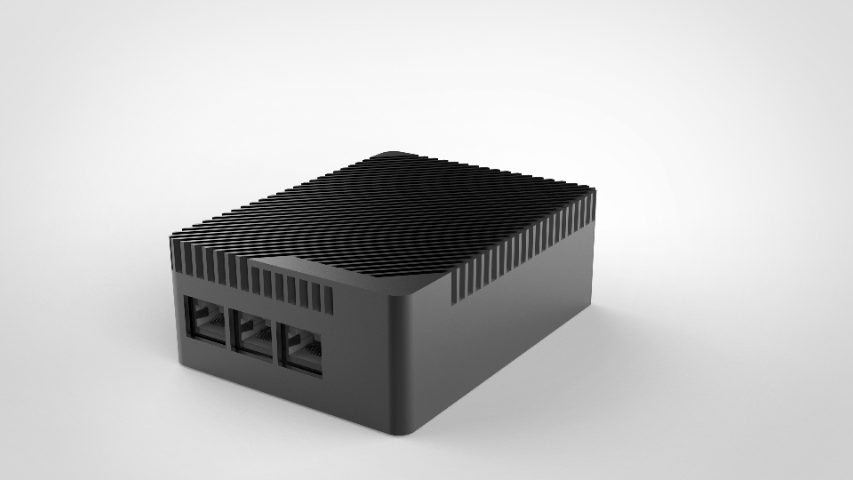

位算單元采用新型電路設計,實現了納秒級的位運算速度。蘇州位算單元定制

RISC-V等開源指令集架構(ISA)的興起,降低了處理器設計的門檻。現在,研究人員和公司可以自由設計基于RISC-V的處理器關鍵,并根據應用需求自定義位算單元的功能和擴展指令。這種開放性促進了創新,催生了眾多針對物聯網、AI等領域的高效處理器設計。確保芯片上數十億個位算單元在制造后全部能正常工作是一項巨大挑戰。設計師會在芯片中插入大量的掃描鏈和內置自測試(BIST)電路。這些測試結構能夠對位算單元進行自動化測試,精確定位制造缺陷,是保證芯片出廠良率和可靠性的關鍵環節。蘇州位算單元定制

- 湖南移動測繪全源融合時空智能敏捷開發平臺供應商 2025-09-20

- 黑龍江競賽用全源融合時空智能敏捷開發平臺解決方案 2025-09-20

- 新疆機器視覺全源融合時空智能敏捷開發平臺二次開發 2025-09-20

- 江蘇邊緣計算位算單元咨詢 2025-09-20

- 上海智能制造開源導航控制器咨詢 2025-09-20

- 合肥教學用全源融合時空智能敏捷開發平臺解決方案 2025-09-20

- 武漢競賽用全源融合時空智能敏捷開發平臺平臺 2025-09-20

- 天津地平線全源融合時空智能敏捷開發平臺應用 2025-09-20

- 內蒙古英偉達全源融合時空智能敏捷開發平臺平臺 2025-09-20

- 無錫機器視覺開源導航控制器開發 2025-09-20

- 青浦區優勢電壓表銷售方法 2025-09-20

- 江蘇高頻集成RFID讀寫器方案 2025-09-20

- 四川中紅外濾光片透鏡 2025-09-20

- 江西汽車維保鋰電池放電儀 2025-09-20

- 紫外光穩定性漫反射目標板應用 2025-09-20

- 單晶硅壓力變送器廠家 2025-09-20

- 上海測量示波器價格 2025-09-20

- 光學積分球檢測儀 2025-09-20

- 青海光纖測溫廠家直銷 2025-09-20

- 重慶進口雙組份點膠設備 2025-09-20