上海sip多芯片封裝

常見芯片封裝類型-DIP:DIP即雙列直插式封裝,是較為早期且常見的封裝形式。它的絕大多數中小規模集成電路芯片采用這種形式,引腳數一般不超過100個。采用DIP封裝的芯片有兩排引腳,可插入具有DIP結構的芯片插座,也能直接焊接在有對應焊孔的電路板上。其優點是適合PCB上穿孔焊接,操作方便;缺點是封裝面積與芯片面積比值大,體積較大。中清航科在DIP封裝業務上技術成熟,能以高效、穩定的生產流程,為對成本控制有要求且對芯片體積無嚴苛限制的客戶,提供質優的DIP封裝產品。芯片封裝需精密工藝,中清航科以創新技術提升散熱與穩定性,筑牢芯片性能基石。上海sip多芯片封裝

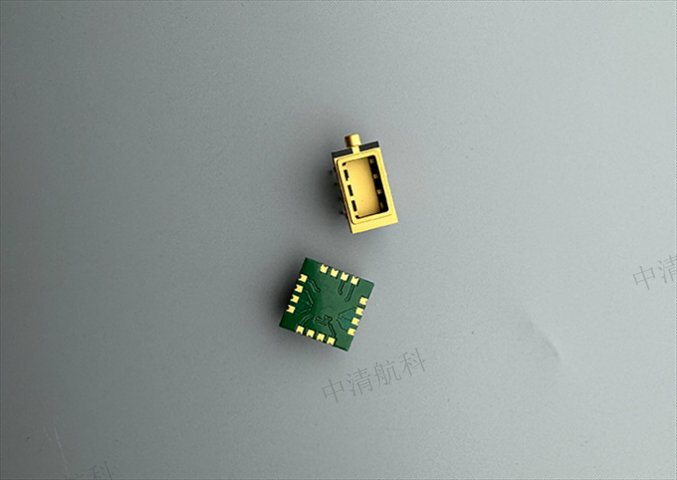

針對5nm芯片200W+熱功耗挑戰,中清航科開發嵌入式微流道冷卻封裝。在2.5D封裝中介層內蝕刻50μm微通道,采用兩相冷卻液實現芯片級液冷。實測顯示熱點溫度降低48℃,同時節省80%外部散熱空間,為AI服務器提供顛覆性散熱方案。基于低溫共燒陶瓷(LTCC)技術,中清航科推出毫米波天線集成封裝。將24GHz雷達天線陣列直接封裝于芯片表面,信號傳輸距離縮短至0.2mm,插損低于0.5dB。該方案使77GHz車規雷達模塊尺寸縮小60%,量產良率突破95%行業瓶頸。浙江ic芯片封裝中清航科芯片封裝方案,適配物聯網設備,兼顧低功耗與小型化。

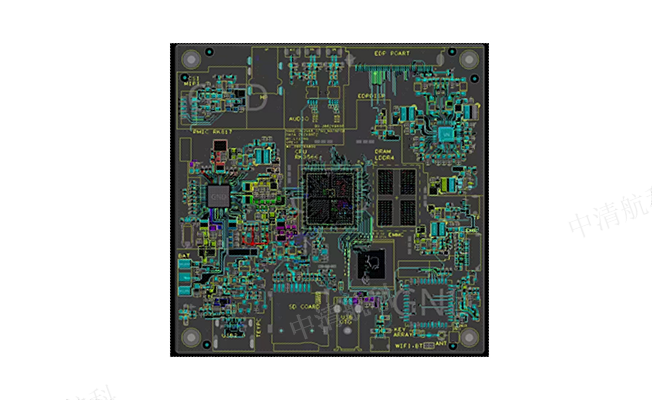

針對車規級芯片AEC-Q100認證痛點,中清航科建成零缺陷封裝產線。通過銅柱凸點替代錫球焊接,結合環氧模塑料(EMC)三重防護層,使QFN封裝產品在-40℃~150℃溫度循環中通過3000次測試。目前已有17家Tier1供應商采用其AEC-QGrade1封裝解決方案。中清航科多芯片重構晶圓(ReconstitutedWafer)技術,將不同尺寸芯片集成于300mm載板。通過動態貼裝算法優化芯片排布,材料利用率提升至92%,較傳統WLCSP降低成本28%。該方案已應用于物聯網傳感器批量生產,單月產能達500萬顆。

芯片封裝的環保要求:在環保意識日益增強的現在,芯片封裝生產也需符合環保標準。中清航科高度重視環境保護,在生產過程中采用環保材料、清潔能源和先進的廢氣、廢水處理技術,減少對環境的污染。公司嚴格遵守國家環保法規,通過了多項環保認證,實現了封裝生產與環境保護的協調發展,為客戶提供綠色、環保的封裝產品,助力客戶實現可持續發展目標。國際芯片封裝技術的發展趨勢:當前,國際芯片封裝技術呈現出集成化、小型化、高頻化、低功耗的發展趨勢。先進封裝技術如3DIC、Chiplet(芯粒)等成為研究熱點,這些技術能進一步提高芯片性能,降低成本。中清航科密切關注國際技術動態,與國際企業和研究機構保持合作交流,積極引進和吸收先進技術,不斷提升自身在國際市場的競爭力,為客戶提供與國際同步的先進封裝解決方案。中清航科芯片封裝技術,支持系統級封裝,實現芯片與被動元件一體化。

面向CPO共封裝光學,中清航科開發硅光芯片耦合平臺。通過亞微米級主動對準系統,光纖-光柵耦合效率>85%,誤碼率<1E-12。單引擎集成8通道112GPAM4,功耗降低45%。中清航科微流控生物芯片封裝通過ISO13485認證。采用PDMS-玻璃鍵合技術,實現5μm微通道密封。在PCR檢測芯片中,溫控精度±0.1℃,擴增效率提升20%。針對GaN器件高頻特性,中清航科開發低寄生參數QFN封裝。通過金線鍵合優化將電感降至0.2nH,支持120V/100A器件在6GHz頻段工作。電源模塊開關損耗減少30%。功率芯片封裝熱密度高,中清航科液冷集成方案,突破散熱效率瓶頸。江蘇mems 芯片封裝

穿戴設備芯片需輕薄,中清航科柔性封裝,適配人體運動場景需求。上海sip多芯片封裝

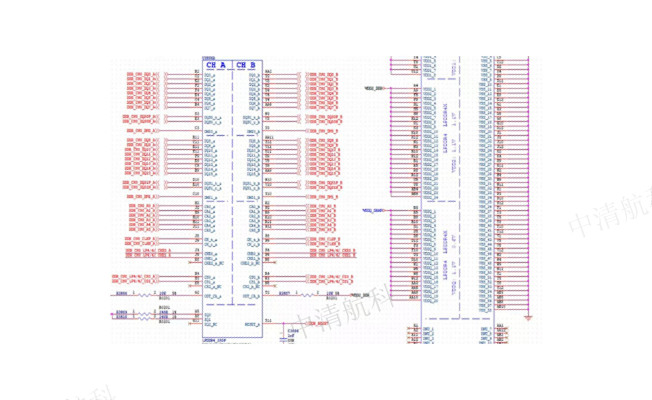

中清航科推出SI/PI協同仿真平臺,集成電磁場-熱力多物理場分析。在高速SerDes接口設計中,通過優化封裝布線減少35%串擾,使112GPAM4信號眼圖高度提升50%。該服務已幫助客戶縮短60%設計驗證周期。中清航科自主開發的AMB活性金屬釬焊基板,熱導率達180W/mK。結合銀燒結工藝的IGBT模塊,熱循環壽命達5萬次以上。在光伏逆變器應用中,另功率循環能力提升3倍,助力客戶產品質保期延長至10年。通過整合CP測試與封裝產線,中清航科實現KGD(已知良品)全流程管控。在MCU量產中采用動態測試分Bin策略,使FT良率提升至99.85%。其汽車電子測試倉溫度范圍覆蓋-65℃~175℃,支持功能安全診斷。上海sip多芯片封裝

- 揚州半導體晶圓切割劃片 2025-09-20

- 江蘇qfp64封裝 2025-09-20

- sip系統級封裝 2025-09-20

- 浙江qfn12封裝 2025-09-20

- 舟山芯片晶圓切割藍膜 2025-09-20

- 上海藍寶石晶圓切割廠 2025-09-20

- 碳化硅切割加工 2025-09-20

- 上海傳感器封裝廠 2025-09-20

- 金華12英寸半導體晶圓切割廠 2025-09-20

- 中芯國際 180流片代理市場報價 2025-09-20

- 上海無人售貨機運營中心 2025-09-20

- 哪里智能硬件操作 2025-09-20

- 智能指環智能戒指性價比 2025-09-20

- 鎮江進口電話交換系統均價 2025-09-20

- 黃浦區小程序開發哪家強 2025-09-20

- 浙江示范項目BIM模型價目表 2025-09-20

- 青浦區品牌網絡營銷企劃 2025-09-20

- 初中物理探究系統排名 2025-09-20

- AI監控識別攝像頭 2025-09-20

- 長沙飛騰主板報價 2025-09-20