武漢EPSON有源晶振采購

面對汽車行駛中的振動沖擊,有源晶振采用加固型內部結構:晶體通過金屬阻尼支架固定,封裝選用耐高溫陶瓷材質并填充防震膠體,可將 2000Hz 振動下的頻率偏移抑制在 ±0.1ppm 以內。這對 ADAS(高級駕駛輔助系統)至關重要 ——ADAS 的毫米波雷達需通過時鐘同步多傳感器數據,振動導致的時鐘偏移會引發目標距離測算誤差,而有源晶振的抗振設計能確保雷達探測精度誤差 < 0.1 米,保障行車安全。針對車載強電磁環境(如電機運轉產生的 EMI、高壓線束輻射),有源晶振集成共模電感與差分輸出接口(如 LVDS),可將電磁干擾對信號的影響降低 90% 以上,相位噪聲在干擾環境下仍穩定在 - 130dBc/Hz(1kHz 偏移),避免干擾車載以太網(100BASE-T1)或 CAN 總線的數據傳輸,防止自動駕駛系統的決策指令延遲。此外,汽車級有源晶振通過 AEC-Q200 可靠性認證,經過高溫老化、溫循、振動等嚴苛測試,MTBF(平均無故障時間)達 100 萬小時以上,可滿足車載設備 “終身免維護” 的需求,適配從車載信息娛樂系統到自動駕駛域控制器的全場景應用。智能穿戴設備空間有限,有源晶振的緊湊設計很適配。武漢EPSON有源晶振采購

有源晶振實現低噪聲輸出的在于底層技術優化:一是選用高純度石英晶體與低噪聲高頻晶體管,晶體的低振動噪聲特性(振動噪聲 < 0.1nm/√Hz)與晶體管的低噪聲系數(NF<1.5dB)從源頭減少噪聲產生;二是內置多級 RC 低通濾波與共模抑制電路,可濾除電源鏈路的紋波噪聲(將 100mV 紋波抑制至 1mV 以下)與振蕩環節的高頻雜波(濾除 100MHz 以上諧波);三是部分型號采用差分輸出架構(如 LVDS 接口),能抵消傳輸過程中的共模噪聲,使輸出信號的幅度噪聲波動控制在 ±2% 以內,相位噪聲在 1kHz 偏移時低至 - 135dBc/Hz,遠優于無源晶振(相位噪聲約 - 110dBc/Hz)。長沙有源晶振多少錢有源晶振輸出信號穩定,減少設備因時鐘問題出現故障。

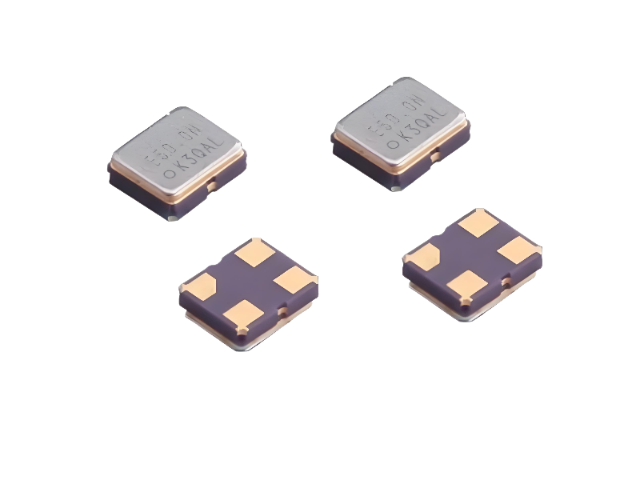

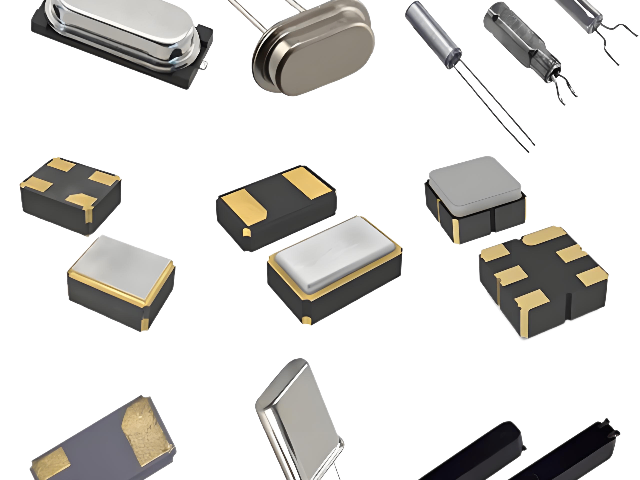

有源晶振的便捷連接特性,從接口、封裝到接線邏輯簡化設備組裝流程,大幅降低操作難度與出錯風險。首先是標準化接口設計,其普遍支持 CMOS、LVDS、ECL 等行業通用輸出接口,可直接與 MCU、FPGA、射頻芯片等器件的時鐘引腳對接 —— 無需像部分特殊時鐘模塊那樣,額外設計接口轉換電路或焊接轉接座,組裝時只需按引腳定義對應焊接,避免因接口不兼容導致的線路修改或元件返工,尤其適合中小批量設備的快速組裝。其次是適配自動化組裝的封裝形式,主流有源晶振采用 SMT(表面貼裝技術)封裝,如 3225(3.2mm×2.5mm)、2520(2.5mm×2.0mm)等規格,引腳布局規整且間距統一(常見 0.5mm/0.8mm 引腳間距),可直接通過貼片機定位焊接,無需手工插裝 —— 相比傳統 DIP(雙列直插)封裝的晶振,省去了穿孔焊接的繁瑣步驟,不僅將單顆晶振的組裝時間從 30 秒縮短至 5 秒,還避免了手工焊接時可能出現的虛焊、錯焊問題,適配消費電子、工業模塊等自動化生產線的組裝需求。

空間優勢在小型化設備中尤為關鍵:例如物聯網無線傳感器(尺寸常 <20mm×15mm),時鐘電路空間節省后,可預留更多空間給射頻模塊或電池,延長設備續航;便攜醫療儀器(如指尖血氧儀)需在緊湊外殼內集成多模塊,有源晶振的 “單元件替代多元件” 特性,能避免 PCB 布局擁擠導致的信號干擾,同時縮小設備整體體積。此外,部分微型有源晶振采用貼片封裝(如 1.6mm×1.2mm),可直接貼裝于 PCB 邊緣或夾層,進一步利用邊角空間,為設備小型化設計提供更大靈活性,尤其適配消費電子、工業控制模塊等對空間敏感的場景。有源晶振助力設備快速獲取時鐘信號,提升研發效率。

有源晶振之所以能直接輸出高質量時鐘信號,在于內置振蕩器與晶體管的協同工作及一體化設計。其內置的振蕩器以高精度晶體諧振器,晶體具備穩定的壓電效應,在外加電場作用下能產生固定頻率的機械振動,進而轉化為電振蕩信號,為時鐘信號提供的頻率基準,有效降低了溫度、電壓波動對頻率的影響,基礎頻率穩定度可達 10^-6 至 10^-9 量級,遠超普通 RC、LC 振蕩器。內置晶體管則承擔著信號放大與穩幅的關鍵職能。振蕩器初始產生的振蕩信號幅度微弱,通常只為毫伏級,難以滿足電子系統需求。低噪聲晶體管會對該微弱信號進行線性放大,同時配合負反饋電路實時調整放大倍數,避免信號因放大過度出現失真,確保輸出信號幅度穩定。部分型號還采用差分晶體管架構,進一步抑制共模噪聲,使輸出信號的相位噪聲優化至 - 120dBc/Hz 以下,大幅提升信號純凈度。汽車電子領域對穩定性要求高,有源晶振可適配應用。江門揚興有源晶振采購

設計藍牙模塊時,選用有源晶振能簡化電路結構。武漢EPSON有源晶振采購

有源晶振無需外部濾波電路輔助,關鍵在于其內部集成了針對性的噪聲抑制模塊,能從源頭濾除干擾,直接輸出符合系統要求的純凈時鐘信號。從電路設計來看,有源晶振內置多層噪聲過濾結構:首先在電源輸入端集成低壓差穩壓單元(LDO)與多層陶瓷濾波電容,可將外部供電鏈路中的紋波噪聲(如消費電子中電池供電的 10-50mV 紋波)抑制至 1mV 以下,避免電源噪聲通過供電端侵入振蕩電路;其次在振蕩與放大單元之間加入 RC 低通濾波網絡,能濾除晶體諧振產生的高頻雜波(如 100MHz 以上的諧波信號),確保進入放大環節的信號純凈度。武漢EPSON有源晶振采購

- 天津YXC有源晶振批發 2025-09-22

- 武漢EPSON有源晶振采購 2025-09-22

- NDK有源晶振應用 2025-09-22

- 東莞YXC有源晶振廠家 2025-09-22

- 西安YXC有源晶振廠家 2025-09-21

- 秦皇島EPSON有源晶振批發 2025-09-21

- 惠州NDK有源晶振代理商 2025-09-21

- 東莞NDK有源晶振應用 2025-09-21

- 東莞揚興有源晶振購買 2025-09-21

- 武漢NDK有源晶振現貨 2025-09-21

- 山西鈹銅彈片價錢 2025-09-22

- 廣東SLM打印機氧氣分析儀推薦廠家 2025-09-22

- 蘇州表面氧化彈片價格咨詢 2025-09-22

- 無錫電鍍錫母排價格 2025-09-22

- 深圳一站式服務展蔚電子涂裝電鍍工藝 2025-09-22

- 連云港新型充電樁銷售供應 2025-09-22

- 工業園區應用可控硅模塊工廠直銷 2025-09-22

- 運城大電流母排報價 2025-09-22

- 湖北IntegratedOptics哪家好 2025-09-22

- 北京矩形航空插頭生產廠家 2025-09-22